# **FPGA based implementation of SDR transceiver**

<sup>1</sup>Yogita S Hon, <sup>2</sup>Vaishali Baste

<sup>1</sup>Assistant Professor, <sup>2</sup>Assistant Professor

<sup>1</sup> Dept. of Electronics and Telecommunication Engg, <sup>1</sup>SNJB's KBJ COE, Chandwad, India.

#### Abstract:

Field Programmable Gate Array (FPGA) based transceiver is purely a new kind of digital implementation of transceiver in Software Defined Radio (SDR) platform. This replaces a multiple platform based system with a single platform. It guarantees reliable, reconfigurable, handy transmitter and receiver. A high-level programming language is used to simulate and implement system in real time.

## Index Terms - Field Programmable Gate Array (FPGA), Software Defined Radio (SDR).

#### **I.INTRODUCTION**

For a conventional discrete component-based design of transceiver, it is not possible to vary the functionality of the system beyond certain range of specification. But a SDR based on FPGA enhances the capability of the platform so as to design a system with reconfigurability and flexibility. It can flexibly alter the radio waves by changing software and without changing SDR platform. SDR can be implemented in different platform. Here, SDR based telecommunication operation is realized in FPGA, using high level programming language. The main application of digital transceiver lies at the test facility of newly developed flight vehicle. A newly developed flight vehicle needs testing. Termination of flight vehicle is mandatory if the high speed vehicle deviates from its preset trajectory due to unpredictable failures of onboard system. FPGA implementation of digital transceiver in SDR platform System is used for termination of high speed flight vehicle under test. Hence at test facility, this system is utilized to secure property and human life. In such cases, specific commands are transmitted from transmitter for termination of test vehicle. The command transmitted is received and decoded by onboard command reception system at flight vehicle and the commanded operation is done accordingly.

## **II.SYSTEM MODEL**

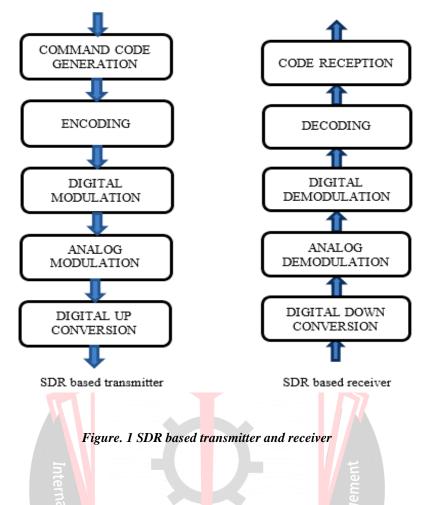

SDR Based Transmitter Algorithm: SDR based transmitter include command code generation, encoding, digital modulation, analog modulation and digital up conversion. The command codes are inputted from personal computer. The generated commands are a frame of N binary bits. The whole frame is encoded with Manchester encoding scheme and total number of bits in a frame becomes double, i.e., 2N. This Manchester encoded binary data waveform modulates a carrier signal using binary frequency shift keying (BFSK) modulation scheme. In this scheme, sinusoidal signal with higher frequency and lower frequency are generated for bit 1 and 0, respectively. This BFSK modulation is done in very low frequency, i.e., in very-low frequency band. This signal is finally upconverted to medium frequency band using frequency modulation (FM) scheme. The basic principle behind FM is to vary the carrier frequency in proportion to the modulating signal. FM modulated signal is the output of command code generator. This signal undergoes digital up conversion (DUC). To improve the sampling frequency of baseband signal interpolation is used. The primary reason to interpolate is to increase the sampling rate at the output of one system, so that another system operating at a higher sampling rate can operate the signal.

SDR Based Receiver Algorithm: In the receiving side, the received signal is down converted using digital down conversion. FM signal can be demodulated by applying the signal to the All-Digital Phase Locked Loop (ADPLL). FM demodulated signal is given to BFSK demodulation block. Finally Manchester decoding is done. Code is received & displayed on PC.

# **III.PROPOSED SYSTEM**

The system is implemented in FPGA. The entire system needs different frequencies for baseband data rate, as sampling frequency for BFSK modulation, as sampling frequency for FM modulation and for CIC interpolation module. The Spartan 3 FPGA board has global clock 30MHz. By using DCM in FPGA and clock generation module, required clocks are generated.

Digital Clock Manager (DCM): Spartan 3 has internal clock frequency of 30MHz. The 100MHz clock is generated from 30MHz clock using digital clock manager. In Xilinx clocking wizard general setup, input 30MHz as input clock frequency and input 100MHz as output clock frequency. All the remaining clocks are generated using clock generation sub module. Initially set count and clock as zero. Then increment the count. Select a value for the count in such a way that input clock period multiplied by that value should give required clock period. When the count equals selected value, take negation of clock and set count equal to zero. Then repeat the steps.

Coding Principles of Manchester Code: Manchester code is mainly used in digital systems. It is used to represent the binary values 0 and 1. It represents the binary values by a transition. The transition occurs at midbit, with low to high transition is used to represent a logic zero, and a high to low represent a logic one. A pattern of consecutive ones or zeros result in a transition on the cell boundary. When the data pattern alternates between one and zero, there is no transition at the cell boundary. Manchester code has no DC component, so it can be transformer coupled. The functions of the encoder section include a microprocessor interface, parallel to serial conversion, frame generation, and Manchester encoding. This circuitry does not require a high-frequency clock. The frame format used is similar to that of a UART.

# **IV.BFSK Modulation**

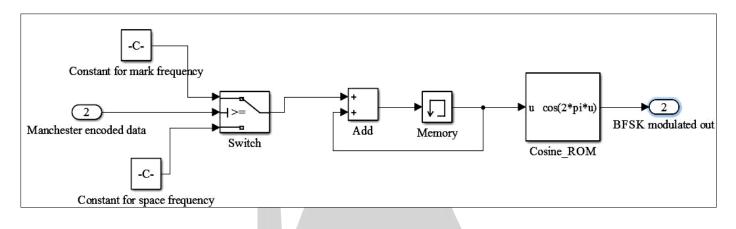

Simulink model for the BFSK modulator is shown in Fig. 2The selected BFSK mark frequency is 50 KHz and space frequency is 10 KHz. By using a switch, if the Manchester encoded output is greater than 0, select constant for BFSK mark frequency and if it is zero, select constant for BFSK space frequency. It is given to the adder based on the output of Manchester encoder. Adder and memory together work as a phase accumulator. Cosine of the phase gives the modulated output.

Figure. 2 BFSK modulation

#### **Block Memory Generator:**

Block memory generator is used to perform both BFSK and FM modulation. Xilinx provides a flexible Block Memory Generator core to create memories running up to 450 MHz. The Block Memory Generator IP core creates optimized block memories for Xilinx FPGAs. Block memory generator is selected from FPGA features and design. Component name is given as sine\_table.

Memory Types: The Block Memory Generator core generates five types of memories: Single-port RAM, Simple Dualport RAM, True Dual-port RAM, Single-port ROM, and Dual-port ROM. Here we need single port ROM.

Selectable Width and Depth: The Block Memory Generator core generates memories with 1 to 4608 bits width, and with depths of two or more words. Here we need to select read width in memory size as 10 bits and read depth in memory size as 32. The data that should be stored in ROM should store as .coe file in the ip core directive of FPGA. In the next step load the .coe file then click finish.

## **Frequency Modulation:**

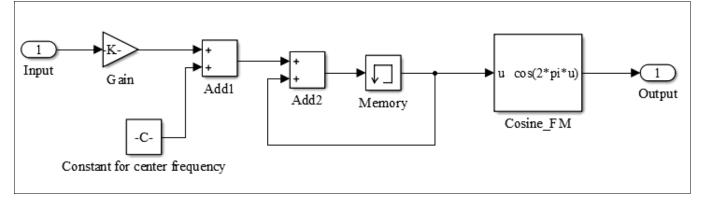

Simulink model for the combined Manchester encoder and FM modulator is shown in Fig. 3. The selected FM deviation is 250 KHz. The output from BFSK modulator is multiplied with a gain K at a sampling rate of 10MHz. A constant for FM deviation equal to 250 KHz is added with gain block output and is given to phase accumulator. Adder and memory together work as a phase accumulator. Cosine of the phase gives the modulated output.

**V.CONCLUSION**

# Figure. 3 Frequency modulator

Proposed SDR-based digital transceiver system can be implemented using Xilinx FPGA, gives a very highly flexible platform for complex algorithms for digital transceiver system designing. The system has been designed using Xilinx software. It provides a very reliable and fast communication. Suitable algorithms for signal generation, encoding, and baseband, and pass band modulation, DUC, DDC, demodulation and decoding of design have been chosen and implemented to ensure optimized uses of hardware.

# REFERENCES

- [1] Amiya Ranjan Panda, Debahuti Mishra, Hare Krishna Ratha, "FPGA Implementation of Software Defined Radio-Based Flight Termination System," IEEE Transactions On Industrial Informatics, Vol. 11, No. 1, February 2015.

- [2] T. Ulversoy, "Software defined radio: Challenges and opportunities," IEEE Commun. Surv. Tuts., vol. 12, no. 4, pp. 531–550, 2010.

- [3] R. Woods, J. McAllister, Y. Yi, and G. Lightbody, "FPGA-Based Implementation of Signal Processing Systems". Hoboken, NJ, USA: Wiley, Oct. 2008, p. 65.

- [4] J. Meier, R. Kelley, B. M. Isom, M. Yeary, and R. D. Palmer, "Leveraging software-defined radio techniques in multichannel digital weather radar receiver design," IEEE Trans. Instrum. Meas., vol. 61, no. 6, pp. 1571 1582, Jun. 2012.

- [5] V. B. Alluri, J. R. Heath, and M. Lhamon, "A new multichannel, coherent amplitude modulated, time-division multiplexed, software-defined radio receiver architecture, and field-programmable-gate-array technology implementation," IEEE Trans. Signal Process., vol. 58, no. 10, pp. 5369–5384, Oct. 2010.

- [6] Spartan-3 FPGA Family Data Sheet, DS099 June 27, 2013.

- [7] Jin Li, YijunLuo, Mao Tian, "FM Stereo Receiver Based on Software-Defined Radio", International Journal of Digital Content Technology and its Applications(JDCTA) Volume6,Number1,January 2012.

- [8] Juan Pablo Martinez Brito, Sergio Bampi "Design of a Digital FM Demodulator based on a 2nd<sup>o</sup> Order All-Digital Phase-Locked Loop ",PGMICRO Graduate Program on Microelectronics.

- [9] N. Jyothi, S. Jayaprakash, and S. K. Gowda, "Design and VLSI implementation of high performance DUC and DDC for software defined radio applications" in Proc. Int. Conf. Emerg. Trends Commun. Control Signal Process. Comput. Appl. (C2SPCA), 2013, pp. 1–3.

- [10] M. Bernard-Schwarz, W. Zwick, L. Wenzel, J. Klier, and M. Groschl, "Field programmable gate array-assigned complex-valued computation and its limits," Rev. Sci. Instrum., vol. 85, no. 9, pp. 093104–093104-6, 2014.