# A Research Paper on Power Optimization of MUX Module

Sharayu Amol Shinde<sup>1</sup>, Dr.M.S.Kumbhar<sup>2</sup>

<sup>1</sup>Student, Rajarambapu Institute of Technology(India), affiliated to Shivaji University, sharayu96@gmail.com <sup>2</sup>Proffesor, Rajarambapu Institute of Technology(India), affiliated to Shivaji University, mahesh.kumbhar@ritinia.edu

# ABSTRACT

This file High speed, low power and less area are the basic needs for any of the digital circuits. In today's world, low power has come out as a principal concept of electronics world. Power optimization has become a key point for the area and performance of VLSI Chip design. With a shrinking technology, over all power management and power optimization are the emerging challenges due to the increased complexity. For many VLSI designs, optimization of power is as important as timing due to the need to extend the battery life and reduce the cost. The design component has conflicting affect on overall performance of circuits. An optimization of power consumption can be achieved by altering different components and parameters of the circuit.

As far as digital circuits concerned, multiplexer is the basic circuitry of any digital circuit. The aim of this paper is to optimize power consumption of a multiplexer module. In this paper, the need of power optimization, techniques of power optimization and the techniques used to optimize the multiplexer modules are discussed. The multiplexer modules are designed in different logic styles and finally this paper has come up with an optimized multiplexer module. Along with the use of different logic styles, one of the parameters i.e. W/L ratio of MOSFET which affects the power consumption is also altered so as to reach the optimum results.

Keywords: Multiplexer, VLSI (Very Large Scale Integration), power optimization, Tanner EDA

### **1. INTRODUCTION**

The increasing complexity and speed of today's designs leads to a significant increase in the power consumption of very-large-scale integration (VLSI) circuits. To meet this requirement, various techniques of designing the circuit and parameters of transistors like power dissipation, switching capacitance, transition activity, and short-circuit currents are being worked upon to reduce power. The power consumption strongly depends upon the logic style used to design the circuit.[21] Depending upon the kind of circuit to be implemented, its application and the design techniques and methodologies used, various performance aspects come into the picture, denying the formation of universal rules for optimal logic styles.

In this paper, 2:1 multiplexer is implemented using CMOS, CMOS transmission gate logic, Pass transistor logic styles and NMOS pass transistor logic. A low power multiplexer is developed referring to the above mentioned logic styles which consume less power compared to the multiplexers designed using those logic styles.

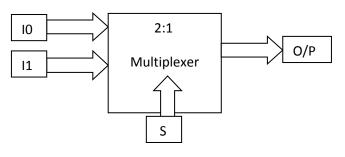

A multiplexer is a device that selects one of many input signals and forwards that particular selected input its output. A multiplexer of n select lines (which selects which input line has to be sent to the output) has 2<sup>n</sup> inputs and one output and hence it is also called a data selector. Multiplexer being a basic circuit can be used to implement any combinational circuit. So by optimizing design of multiplexer, many combinational circuits can be power optimized. Below figures show the block diagram and truth table for 2:1 multiplexer given below.

Figure 1.1 2:1 MUX

### Table.1.1 Truth table for 2to1 multiplexer

| S | OUT |

|---|-----|

| 0 | 10  |

| 1 | 11  |

#### 2. **Power Consumption Concepts**

#### 2.1 **Power Management**

Power consumption concern comes into the picture when the portable electronic systems started coming up. In these systems, the battery lifetime is a necessary element for the commercial success of the product[5]. A high absolute level of power is not just undesirable, but also it leads to heat dissipation. Thus to keep the system in a working condition at acceptable temperatures, systems may require heat removal system in turn adding to the circuitry and cost of the systems. Hence power management plays a key role in almost every aspect of an electronic system.

#### 2.2 **Benefits of Power Optimization**

Power consumption provides many benefits such as less heat is generated, which overcome many problems associated with high temperature, such as the need for heat sinks. This in turn provides low cost product to the consumer. As heat dissipation is reduced, the reliability of the system is increased due to lower temperature stress gradients on the device[15]. The extended life of the battery in battery-powered systems is achieved.

#### 2.3 Sources of Power Consumption

There are primarily three main causes of power dissipation in the digital circuits:

- A] Static Power Dissipation

- B] Dynamic Power Dissipation

- C] Short-Circuit Power Dissipation

# A] Static Power Dissipation

The static power components come into play when the circuits are at rest, i.e. when there is no supply to ye circuit or they are biased to a specific state or there is no activity in the circuits. The static power dissipation consists of reversed-biased diode leakage and sub threshold currents. Because of necessity of down-scaling of threshold voltages, the sub threshold leakage becomes more and more pronounced[21]. In weak inversion, below the threshold voltage, the transistors do not turn completely off. The sub threshold current depends on the threshold voltage. Dynamic power is only when there is switching but static power is permanent[9].

Research in Engineering A

Eqn 2.3.a

Ps= Ileakage \* Vdd

where.

Ileakage : Leakage current

V<sub>dd</sub>: Supply Voltage

**B**] Dynamic Power Dissipation

Dynamic power dissipation depends on the activity, timing, output capacitance, and supply voltage of the circuit. The repeated charging and discharging of the output capacitance is necessary to transmit information in CMOS circuits. This charging and discharging of the node capacitances causes for the switched power dissipation[25].

$P_{dyn} = C_L \cdot V_{dd}^2 \cdot f$

Eqn 2.3.b

where.

CL: Load Capacitance

V<sub>dd</sub>: Supply Voltage

f: frequency of the input signal

### C] Short Circuit Power Dissipation

In real time circuit operations, signals have non-zero rise and fall times which causes both the P and N networks of the CMOS circuit to conduct simultaneously i.e. both nmos and pmos transistors may conduct simultaneously for short amount of time during switching. This current is called short circuit current consumption and it does not contribute to the charging/discharging of the capacitance in the circuit. This component is especially prevalent if the input signal rise time and fall times are large or/and the output load capacitance is small[29].

P<sub>sc</sub>= I<sub>mean</sub> \* V<sub>dd</sub>

Eqn2.3.c

where,

I<sub>mean</sub> = average current

V<sub>dd</sub> = Supply Voltage

### 2. 4 Optimization Techniques in VLSI

The power optimization in VLSI is mainly done by the following techniques

• Transistor sizing: In this technique the size (width and length) of each gate is altered for minimum power usage. Transistor sizing in a combinational gate circuit has pronounced effect on power dissipation and circuit delay[11]. As the size of the transistors in a given gate increases, the delay of the transistor decreases, but the power dissipated increases.

• Power gating: High threshold voltage sleep transistors are used in this technique. They cut-off a circuit block when the block is not in dynamic state i.e. it is not switching. An important design parameter is sleep transistor sizing. This helps reducing the stand-by or leakage power[14].

Logic

styles: Using different types of logics such as cmos logic, transmission gate logic, pass transistor logic, pseudo nmos logic, etc. According to the requirement of the applications, various logics can be implemented based on speed, area, power.

• Voltage scaling: Voltage at which the component works is increased or decreased without affecting the end result of the circuit[27]. Voltage scaling is again divided into three categories static voltage scaling, dynamic voltage scaling and adaptive voltage scaling. Though lower supply voltages use less power, the delay increases.

• Voltage islands: Separate blocks are run at different voltage levels for saving power. Level-shifters are used so that when two blocks with different supply voltages are present, they communicate with each other through it.

• Variable VDD: The supple voltage of a single block is varied during operation, high voltage (and high power) when the block needs to go fast and low voltage when slow operation is acceptable.

• Multiple threshold voltages: Latest techniques can help build transistors with varying threshold voltages. Combination with number of different threshold voltages of CMOS transistors can save power[17].

# 3. Methods Adopted for Power Optimization

# 3.1 Logic Styles Used For MUX Modules

In this paper, MUX modules are first designed conventionally using the logic styles like CMOS logic, NMOS Pass Transistor Logic, Pass Transistor Logic and Transmission gate Logic. Towards the end of this section, optimized MUX module is being discussed.

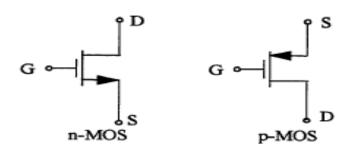

A] CMOS Logic Style

The fundamental building blocks of CMOS circuits are P-type and N-type MOSFET transistors. A P-type MOSFET can be modeled as a switch that is closed when the input voltage is low (0 V) and open when the input voltage is high (5 V). A N-type MOSFET can be modeled as a switch that is closed when the input voltage is high (5 V) and open when the input voltage is low (0 V). The basic idea for CMOS technology is to combine P-type and N-type MOSFETs such that there is never a conducting path from the supply voltage (5 V) to ground[13]. As a

consequence, CMOS circuits consume very little energy. The symbol for an n-channel transistor and p- channel transistor are shown in figure below.

Fig. 3.1.a NMOS Transistor Fig. 3.1.b PMOS Transistor

B] Pass Transistor Logic and NMOS Pass Transistor Logic

In electronics, pass transistor logic (PTL) describes several logic families used in the design of integrated circuits. It reduces the count of transistors used to make different logic gates, by eliminating redundant transistors[6]. Transistors are used as switches to pass logic levels between nodes of a circuit, instead of as switches connected directly to supply voltages. This reduces the number of active devices, but has the disadvantage that the difference of the voltage between high and low logic levels decreases at each stage. Each transistor in series is less saturated at its output than at its input[16]. Pass transistor logic often uses fewer transistors, runs faster, and requires less power than the same function implemented with the same transistors in fully complementary CMOS logic.

C] NMOS-Pass Transistor:

The gate of both the transistors is static. A low-impedance path exists to both supply rails under all circumstances. N numbers of transistors are required instead of 2N that in CMOS logic style. Power consumption is less compared to that of the CMOS logic style[3]. In this logic style, the transistors work bidirectionally (versus that in CMOS logic style which is unidirectional).

There are two types of pass transistors: i. NMOS Pass: Passes strong logic '1' and weak logic '0' ii.PMOS Pass: Passes strong logic '0' and weak logic '1'

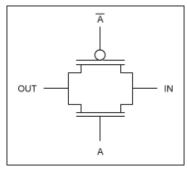

D] Transmission Gate Logic

The Transmission Gate, (TG) is a bilateral switch, which is not possible with a single MOS device. TGL can have either of its terminals can be the input or the output. As well as the input and output terminals, the transmission gate has a third connection called the control, where the control input determines the switching state of the gate as an open or closed (NO/NC) switch. The advantage of using both in an arranged network is that the P-type MOSFET passes strong logic 1 and weak logic 0 and P-type MOSFET passes strong logic 0 and weak logic 1[12]. Hence we get both i.e. strong logic 1 and logic 0.Therefore, connecting an NMOS transistor with a PMOS transistor in parallel provides a single bilateral switch which offers efficient output drive capability for CMOS logic gates controlled by a single input logic level. The symbol of TGL is given below.

Fig. 3.1.c Transmission Gate Logic Transistor

E] Optimized Module

The optimized MUX module is designed using the CMOS logic style with the addition of a PMOS connected at the bottom end of the CMOS MUX module as a pull-down sleep transistor and the output drives its gate. The optimized module works similarly to that of the conventional CMOS module. But the difference is the output is obtained only if the value of the output is high (logic 1) therefore supplying the gate of PMOS sleep transistor with a high logic. This high logic turns the PMOS off and hence the output is obtained as it is. Otherwise the whole circuit remains off irrespective of the input. This means that the circuit remains off for any low input and turns on only if output is high.

This ensures that the circuit remains in off state except for when the output is high thus lowering the power consumption by the circuit. The circuit consumes power only when the output is high. The truth table for optimized 2:1 MUX module is given as follows:

| S | Input | OUT |

|---|-------|-----|

| 0 | 10= 0 | 0   |

|   | I0= 1 | 1   |

| 1 | I1=0  | 0   |

|   | 11=1  | 1   |

# Table3.1.a. Truth Table of Optimized MUX Module

### 3.2 Power Analysis

To calculate the power theoretically, the following given formulae were used:

| 1. Gate capacitance                                        |           |  |

|------------------------------------------------------------|-----------|--|

| C <sub>G</sub> = W.L.C <sub>OX</sub>                       | Eqn 3.2.a |  |

| 2. Diffusion capacitances                                  |           |  |

| C <sub>diff</sub> =Cj·L·W + Cjsw·(2L+W) + Cjgate·W         | Eqn 3.2.b |  |

| 3. Gate Overlap Capacitance                                |           |  |

| $C_o = C_{OX} \cdot x_d$                                   | Eqn 3.2.c |  |

| where,                                                     |           |  |

| W= width of gate                                           |           |  |

| L= length of gate                                          |           |  |

| C <sub>OX</sub> = Capacitance of oxide layer               |           |  |

| Cj= Junction Capacitance                                   |           |  |

| Cjsw= Side wall Junction Capacitance                       |           |  |

| Cjgate=Gate Junction Capacitance                           |           |  |

| x <sub>d</sub> = thickness of gate and drain/source layers |           |  |

| Load Capacitance is given as:                              |           |  |

| $C_L = C_G + C_{diff} + C_o$                               | Eqn 3.2.c |  |

The power results are obtained by simulation of the MUX Modules on Tanner EDA Tool on 250nm of technology. The results of simulation are displayed in the Results section.

### 4. Results

The power consumed by all types of MUX modules is analyzed by both theoretical as well as simulation method.

### Theoretical Analysis

The power of each MUX module is calculated by using the following mathematical formulae:

| i. $P_{dyn} = C_L \cdot V_{dd}^2 \cdot f$ |                                                            | from <b>Eqn2.3.2</b>  |

|-------------------------------------------|------------------------------------------------------------|-----------------------|

| ii.                                       | $C_L = C_G + C_{diff} + C_o$                               | from <b>Eqn 3.2.c</b> |

| iii.                                      | C <sub>G</sub> = W.L.C <sub>OX</sub>                       | from <b>Eqn 3.2.a</b> |

| iv.                                       | v. C <sub>diff</sub> =Cj·L·W + Cjsw·(2L+W) + Cjgate·W from |                       |

|                                           |                                                            | Eqn 3.2.b             |

| ۷.                                        | $C_o = C_{OX} \cdot x_d$                                   | from Eqn 3.2.c        |

By calculating the above mentioned capacitances we dynamic power mentioned in table 4.1.

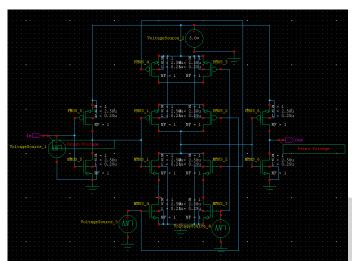

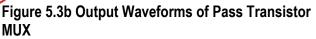

Following are the schematics and output waveforms of the simulated MUX Modules.

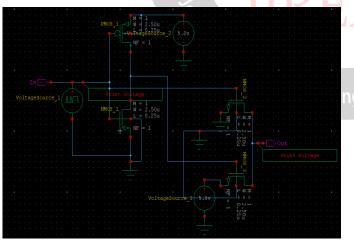

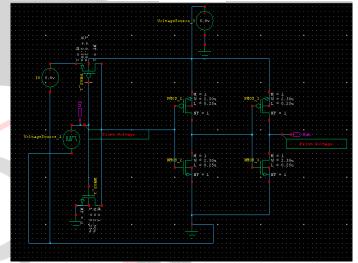

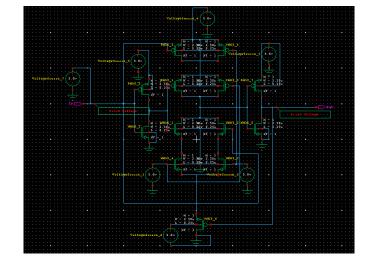

Figure 5.1a Schematic of CMOS MUX

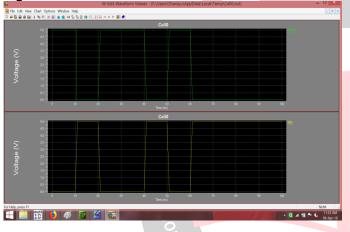

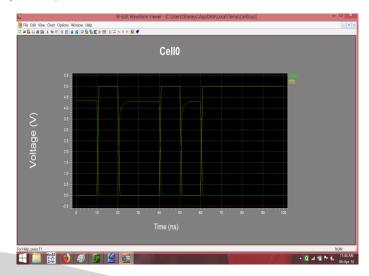

Figure 5.1b Output Waveforms of CMOS MUX

Figure 5.2a Schematic of NMOS MUX

Figure 5.3a Schematic of Pass Transistor MUX

# Figure 5.4b Output Waveforms of TGL NMOS MUX

Figure 5.5a Schematic of Optimized MUX

Here are the results obtained by simulation done on Tanner EDA on 250nm of technology. **Table 4.1 Power Results**

| Sr.No | Logic Style | Power simulated (W) | Power calculated (W) |  |

|-------|-------------|---------------------|----------------------|--|

| 1.    | CMOS        | 5.980564e-006       | 6.75-006             |  |

| 2.    | NMOS        | 7.572388e-006       | 11.25e-006           |  |

| 3.    | PTL         | 1.188082e-006       | 3.28e-006            |  |

| 4.    | TGL         | 2.553231e-006       | 3.73e-006            |  |

| 5.    | OPT         | 7.565226e-009       | 2.03e-006            |  |

# 5. Conclusion

In this paper the challenge of power optimization of 2:1 MUX module on 250nm technology was taken up and resolved. After studying various methods and techniques for power optimization, one way that is developing MUX module using different logic styles was finalized and worked upon. The optimized module of MUX developed on 250nm consumes the minimum power amongst all the other modules. Further, the optimized MUX module can be optimized by altering various parameters like W/L ratio, threshold voltages, etc according to the need of the application.

# 6. References:

[1] Powell, S. et al., 1990. "Estimating power dissipation of VLSI signal processing chips: The PFA technique".VLSI Signal Processing IV, pp: 250-259.

[2] Anantha P. Chandrakasan, 1994. "Low-Power Digital CMOS Design" PhD thesis, University of California at 13. Berkeley, UCB/ERL Memorandum No. M94/65.

[3] Catthoor, F., et al., 1994. "Global communication and memory optimizing transformations for low power signal processing systems". In IEEE workshop on VLSI signal processing, La Jolla, CA, Oct.

[4] Chatterjee, A. and R. Roy, 1994 "Synthesis of low power linear DSP circuits using activity metrics", In International Conference on VLSI Design, India.

[5]S.C.Prasad and K.Roy "Circuit Optimization for Minimization of Power Consumption under Delay Constraint". In Proceedings of the Int'l Workshop on Low Power Design, pages 15–20, April 1994.

[6] S. C. Prasad and K. Roy. "Circuit Optimization for Minimization of Power Consumption Under Delay Constraint". In Proceedings of the Int'I Workshop on Low Power Design, pages 15–20, April 1994.

[7] Chren, W.A., 1995, "Low Delay-Power Product CMOS Design Using One-Hot Residue Coding" In Proceedings of the Int'l Symposium on Low Power Design.

[8] Coello, Carlos A., Christiansen, Alan D. & Hernández Aguirre, "Using Genetic Algorithms to Design Combinational Logic Circuits." ANNIE'96. Intelligent Engineering through Artificial Neural Networks, Volume 6. Smart Engineering Systems: Neural Networks, Fuzzy Logic and Evolutionary Programming. Edited by Cihan H. Dagli, Metin Akay, C. L. Philip Chen, Benito R. Fernandez and Joydeep Ghosh. pp. 391-396. November, 1996.

[9] Coello, Carlos Artemio Coello. "An Empirical Study of Evolutionary Techniques for Multi-objective Optimization in Engineering Design". Ph.D. Dissertation, Department of Computer Science, Tulane University, New Orleans, LA, 1996.

[12] MASSOUD PEDRAM, HIRENDU VAISHNAV, "Power Optimization in VLSI Layout: A Survey" Journal of VLSI Signal Processing 15, 221–232 (1997) °c 1997 Kluwer Academic Publishers. Manufactured in The Netherlands.

[13]Arjit Raychowdhury, Saibal Mukhopadhyay and Kaushik Roy. "Modeling and estimation of leakage in sub90nm devices" In Int. Conf. VLSI Design, pages 65-70, 2004.

[14] Zamin Ali Khana ,S. M. Aqil Burneyb, , Jawed Naseemc, Kashif Rizwand, "Optimization of Power Consumption in VLSI Circuit", IJCSI International Journal of Computer Science Issues, Vol. 8, Issue 2, March 2011, ISSN (Online): 1694-0814

[15] M. Borah, R. M. Owens and M. J. Irwin. "Transistor sizing for minimizing power consumption of CMOS circuits under delay constraint. "In Proceedings of the 1995 International Symposium on Low Power Design, pages 167-172, April 1995. IJCSI International Journal of Computer Science Issues, Vol. 8, Issue 2, March 2011

[16] Zamin Ali Khan ,S. M. Aqil Burney, , Jawed Naseem, Kashif Rizwan , "Optimization of Power Consumption in VLSI Circuit" IJCSI International Journal of Computer Science Issues, Vol. 8, Issue 2, March 2011 ISSN (Online): 1694-0814

[17] Power estimation techniques for embedded and VLSI system: A survey R.Prabakaran1, S. Arivazhagan2 and S.Prabakaran3 Elixir International Journal Elixir Elec. Engg. 53 (2012) 12005-12022 ISSN 2229-712X

[18] Saradindu Panda1, A.Banerjee, B.Maji, Dr.A.K. Mukhopadhyay, "Power and Delay Comparison" Different types of Full Adder Circuits International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering Vol. 1, Issue 3, September 2012 ISSN 2278 - 8875

[19] R.Prabakaran, S. Arivazhagan and S.Prabakaran, "Power estimation techniques for embedded and VLSI system: A survey", R.Prabakaran et al./ Elixir Elec. Engg. 53 (2012) 12005-12022

[20] Meenakshi Mishra • Shyam Akashe, "High performance, low power 200 Gb/s 4:1 MUX with TGL in 45 nm technology", Received: 17 September 2012 / Accepted: 25 February 2013 / Published online: 16 March 2013, The Author(s) 2013. Springerlink.com

[21] M. Jasmin, "Optimization Techniques for Low Power VLSI Circuits", Middle-East Journal of Scientific Research 20 (9): 1082-1087, 2014 ISSN 1990-9233 Publications, 2014

[22] Anuj, Divya Khanna, "A Literature Review on Design Strategies and Methodologies of Low Power VLSI Circuits", IOSR Journal of VLSI and Signal Processing (IOSR-JVSP) Volume 4, Issue 2, Ver. IV (Mar-Apr. 2014), PP 17-21 e-ISSN: 2319 – 4200, p-ISSN No. : 2319 – 4197

[23] Neha Thakur 1, Deepak Kumar, "Review Paper on Low Power VLSI Design Techniques", International Journal of Electrical Electronics & Computer Science Engineering Volume 1, Issue 4 (August 2014), ISSN : 2348 2273

[24] Ambily Babu, "Power Optimization Techniques at Circuit and Device Level in Digital CMOS VLSI – A Review", International Journal of Engineering Research & Technology (IJERT) Vol. 3 Issue 11, November-2014, ISSN: 2278-0181

[25] Narinder Sharma" Comparison of adiabatic and Conventional CMOS" ISSN : 2394 – 2231 International Journal of Computer Techniques - Volume1 Issue 2 Dec - 2014International Journal of Computer Techniques - Volume1 Issue 2 Dec - 2014

[26] Neha Thakur, Deepak Kumar, "Review Paper on Low Power VLSI Design Techniques" International Journal of Electrical Electronics & Computer Science Engineering Volume 1, Issue 4 (August 2014), ISSN 2348 2273

[27] Ambily Babu, "Power Optimization Techniques at Circuit and Device Level in Digital CMOS VLSI- A Review", International Journal of Enginnering Research and Technology (IJERT), Vol 3 Issue 11, November 2014, ISSN 2278-0181

[28] Paras Gupta1, Pranjal Ahluwalia, Kanishk Sanwal, Peyush Pande, "Performance Comparison Of Digital Gates Using Cmos And Pass Transistor Logic Using Cadence Virtuoso" International Journal of Science, Technology & Management Volume No.04, Issue No. 01, January 2015 ISSN (online): 2394-1537

[29] Pankaj Gautam, Devesh Kaushik, Rahul Sharma "Design of CMOS Inverter Using Different Aspect Ratios" International Journal of Scientific Research Engineering & Technology (IJSRET) ISSN: 2278–0882 EATHD-2015 Conference Proceeding, 14-15 March, 2015

[30] Józef Kulisz, Mirosław Chmiel, Adrian Krzyżyk, Marcin Rosół, " A Hardware Implementation of Arithmetic Operations for an FPGA-based Programmable Logic Controller", © 2015, IFAC (International Federation of Automatic Control) Hosting by Elsevier Ltd. All rights reserved.

[31] Sumita Gupta, Sukanya Padave, "Power Optimization for Low Power VLSI Circuit", International Journal of Advanced Research in Computer Science and Software Engineering, volume 6, Issue 3, March 2016 ISSN: 2277 128X

[32] Sumita Sukanya Padave "Power Optimization for Low Power VLSI Circuits" International Journal of Advanced Research in Computer Science and Software Engineering Volume 6, Issue 3, March 2016 ISSN: 2277 128X Special Issue on 3rd International Conference on Electronics & Computing Technologies-2016

[33] H. J. M. Veendrick, "Short-circuit dissipation of static CMOS circuit and its impact on the design of buffer circuits," IEEE J. Solid-State Circuits, Vol. 19, Aug., 1984, pp. 468-473.

[34] Devadas, S., A. Ghosh and K. Keutzer, 1994. ""Logic Synthesis. McGraw Hill, New York, N.Y.

[35] Rakesh Mehrotra, Massoud Pedram Xunwei Wu, "Comparison between nMOS Pass Transistor logic style vs. CMOS Complementary Cells", This work was supported in part by DARPA under contract #F33615-95-C-1627.